中国科大高速VCO模数转换器芯片实现2.5 GS/s采样速率

近日,中国科学技术大学集成电路学院胡诣哲教授课题组在高速VCO-based ADC芯片研究中取得重要进展。团队提出一种基于可复位环形压控振荡器的新型模数转换器架构(R-RVCO-based ADC),实现了最高2.5 GS/s采样速率的高性能数据转换,突破了相关架构在高速应用中的关键瓶颈。相关研究成果以“A 0.5–2.5-GS/s Resettable Ring-VCO-Based ADC Eliminating Quantization-Noise Shaping”为题,发表于集成电路领域国际著名期刊《IEEE Journal of Solid-State Circuits》(JSSC)。

随着人工智能(AI)以及超高速无线、有线互联技术的快速发展,面向GHz级带宽信号处理的高速模数转换器(ADC)需求日益迫切。与此同时,先进CMOS工艺正持续向低电压、高集成度方向演进,传统依赖模拟放大器的ADC架构在速度、功耗和工艺可扩展性等方面面临严峻挑战。因此,基于压控振荡器的模数转换器(VCO-based ADC)凭借高度数字化、结构简洁以及对先进工艺的良好适应性,正成为实现高性能数据转换的重要技术方向。然而,其工作频率长期难以突破GHz级瓶颈,成为制约该类架构进一步发展的关键问题。

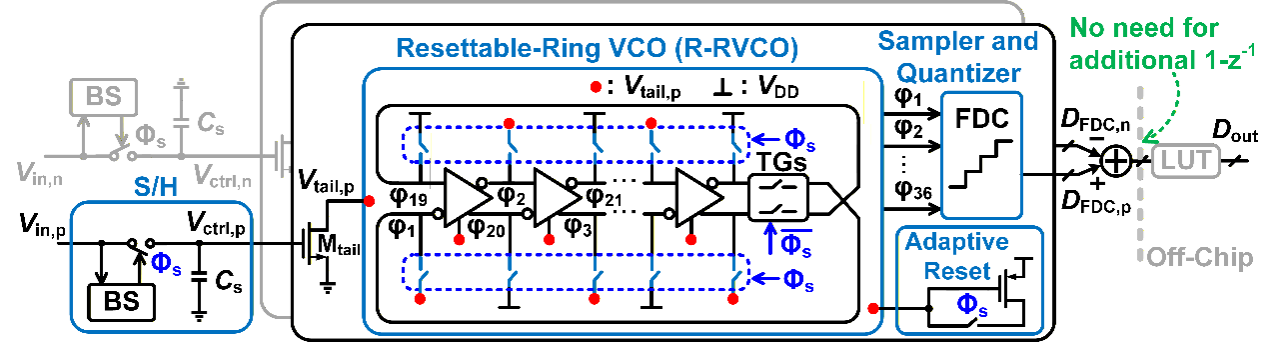

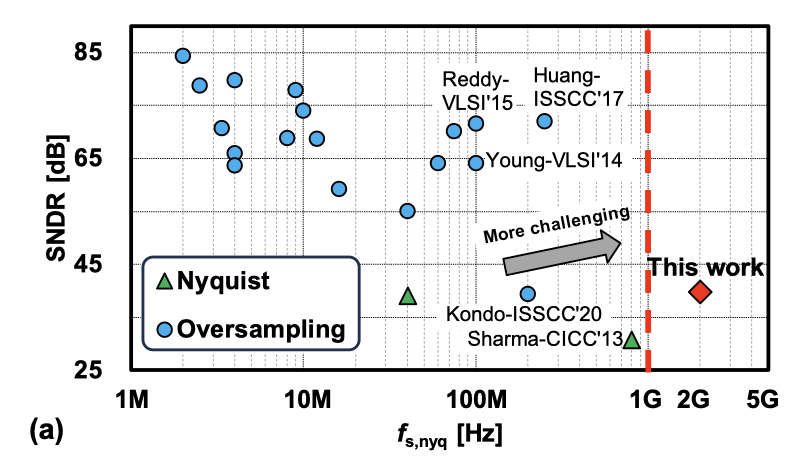

针对传统VCO-based ADC在奈奎斯特采样条件下面临的相位噪声积分效应和量化噪声受限问题,研究团队从理论分析与架构设计两个层面开展了系统研究。团队建立了统一的行为级模型与噪声分析框架,对多类VCO-based ADC进行了等效建模和噪声推导,揭示了制约VCO-based ADC采样速率提升的关键瓶颈。据此,团队提出一种离散时间开环R-RVCO-based ADC结构(见图1),通过在VCO内部引入差分传递特性,无需额外微分器即可有效抑制相位噪声积分效应,同时避免奈奎斯特带内的量化噪声整形,使信噪比提升约3dB。

图1 提出的高速VCO-based ADC架构图与性能对比图

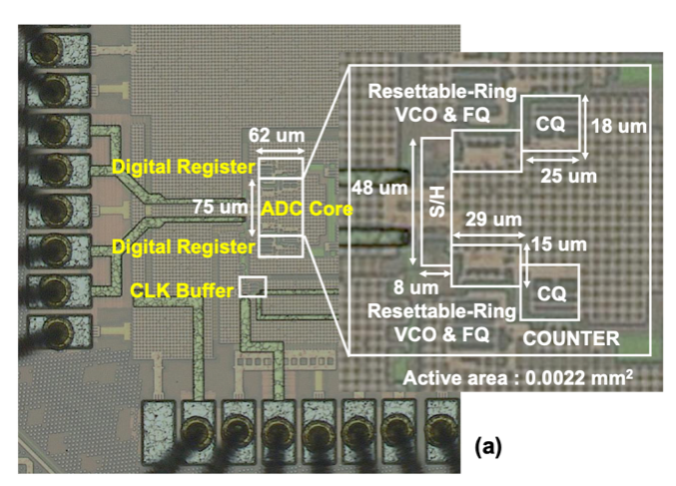

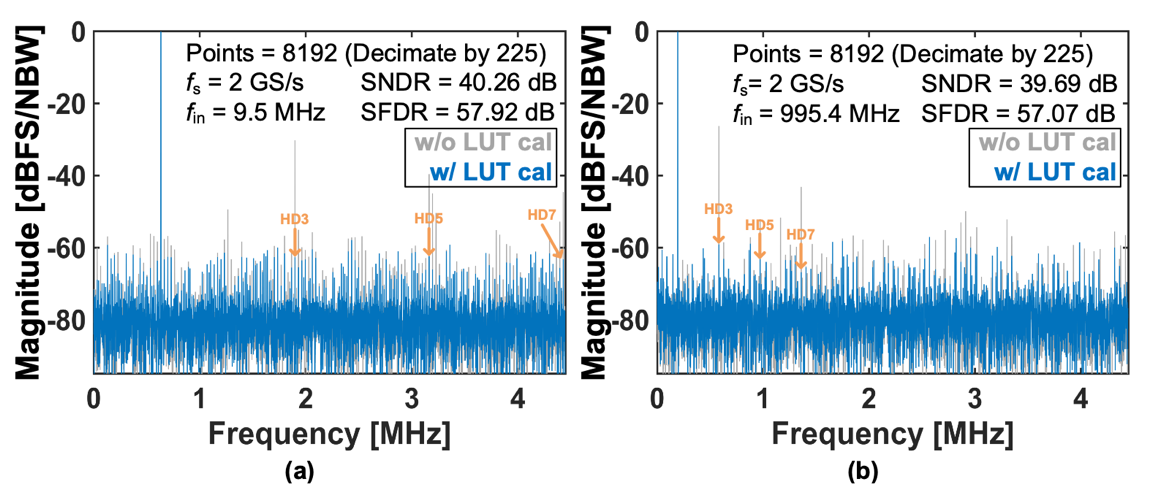

此外,该架构无需数字差分模块,进一步提高了系统对触发器亚稳态的容忍度和整体鲁棒性。在电路实现方面,团队提出了自适应重置技术,实现了VCO重置电压与振荡摆幅的精确匹配;同时,在粗量化器和细量化器中分别引入动态开关缓冲结构与相位折叠技术,以提高相位提取效率并有效降低硬件开销。该芯片基于22nm CMOS工艺实现(见图2),核心面积仅0.0022 mm⟡,支持500 MS/s至2.5 GS/s的采样速率范围。在2 GS/s采样速率下,实测信噪失真比(SNDR)达到39.1 dB,Walden能效指标(FoM_W)低至31.3 fJ/conv.-step。

图2 芯片图与测试结果

集成电路学院博士生鲁涛为论文第一作者,胡诣哲为通讯作者。该研究工作得到了安徽省集成电路科学与技术重点实验室的支持。

论文链接:https://ieeexplore.ieee.org/document/11429661

(科研部、集成电路学院、微电子学院)